PCIe 7.0 Draft 0.5 Spec Available: 512 GB/s over PCIe x16 On Track For 2025

by Anton Shilov on April 4, 2024 8:00 AM EST

PCI-SIG this week released version 0.5 of the PCI-Express 7.0 specification to its members. This is the second draft of the spec and the final call for PCI-SIG members to submit their new features to the standard. The latest update on the development of the specification comes a couple months shy of a year after the PCI-SIG published the initial Draft 0.3 specificaiton, with the PCI-SIG using the latest update to reiterate that development of the new standard remains on-track for a final release in 2025.

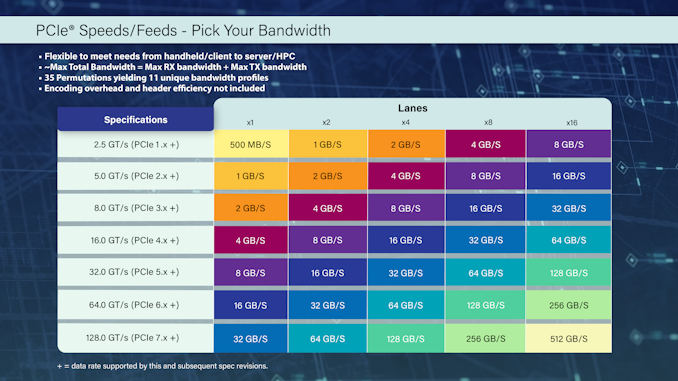

PCIe 7.0 is is the next generation interconnect technology for computers that is set to increase data transfer speeds to 128 GT/s per pin, doubling the 64 GT/s of PCIe 6.0 and quadrupling the 32 GT/s of PCIe 5.0. This would allow a 16-lane (x16) connection to support 256 GB/sec of bandwidth in each direction simultaneously, excluding encoding overhead. Such speeds will be handy for future datacenters as well as artificial intelligence and high-performance computing applications that will need even faster data transfer rates, including network data transfer rates.

To achieve its impressive data transfer rates, PCIe 7.0 doubles the bus frequency at the physical layer compared to PCIe 5.0 and 6.0. Otherwise, the standard retains pulse amplitude modulation with four level signaling (PAM4), 1b/1b FLIT mode encoding, and the forward error correction (FEC) technologies that are already used for PCIe 6.0. Otherwise, PCI-SIG says that the PCIe 7.0 speicification also focuses on enhanced channel parameters and reach as well as improved power efficiency.

Overall, the engineers behind the standard have their work cut out for them, given that PCIe 7.0 requires doubling the bus frequency at the physical layer, a major development that PCIe 6.0 sidestepped with PAM4 signaling. Nothing comes for free in regards to improving data signaling, and with PCIe 7.0, the PCI-SIG is arguably back to hard-mode development by needing to improve the physical layer once more – this time to enable it to run at around 30GHz. Though how much of this heavy lifting will be accomplished through smart signaling (and retimers) and how much will be accomplished through sheer materials improvements, such as thicker printed circuit boards (PCBs) and low-loss materials, remains to be seen.

The next major step for PCIe 7.0 is finalization of the version 0.7 of specification, which is considered the Complete Draft, where all aspects must be fully defined, and electrical specifications must be validated through test chips. After this iteration of the specification is released, no new features can be added. PCIe 6.0 eventually went through 4 major drafts – 0.3, 0.5, 0.7, and 0.9 – before finally being finalized, so PCIe 7.0 is likely on the same track.

Once finalized in 2025, it should take a few years for the first PCIe 7.0 hardware to hit the shelves. Although development work on controller IP and initial hardware is already underway, that process extends well beyond the release of the final PCIe specification.

Source: PCI-SIG

17 Comments

View All Comments

bernstein - Thursday, April 4, 2024 - link

The funny thing is, *while gaming* even an RTX 4090 won’t saturate a PCIe 7.0 x1 link.We can probably drop pcie x16 for anything but datacenters cpu/mainboards… Reply

skaurus - Thursday, April 4, 2024 - link

Even PCIe 5.0 requires more expensive motherboards. PCIe 6.0 is, from what I gather, unlikely to make it even more difficult, but PCIe 7.0 will. Maybe it won't make it into consumer devices at all. Replykpb321 - Thursday, April 4, 2024 - link

Yeah. I don't know if PCI-E 7 will ever make it to consumer boards. If it does it will most certainly used to drive things with fewer lanes. Maybe we will see it as the link between the CPU and the chipset to allow a higher bandwidth connection there but even that seems unlikely. I have no idea where they are going to go for PCI-E 8 if they want to double performance again. Replynandnandnand - Friday, April 5, 2024 - link

I didn't realize that, or forgot, but sounds like that's right.https://www.anandtech.com/show/17203/pcie-60-speci...

"PCIe 6.0 will have the same 36dB loss as PCIe 5.0, meaning that while trace lengths aren’t officially defined by the standard, a PCIe 6.0 link should be able to reach just as far as a PCIe 5.0 link. Which, coming from PCIe 5.0, is no doubt a relief to vendors and engineers alike."

So PCIe 6.0 can come to consumer products relatively quickly. Reply

bernstein - Thursday, April 4, 2024 - link

Well overall the rtx4090 is 2% slower on pcie 3 x16 so i guess onnsome games it can saturates a pcie x7 x1 link. But i doubt even a rtx 5090 can saturate a pcie 7 x2 linkhttps://tpucdn.com/review/nvidia-geforce-rtx-4090-... Reply

PeachNCream - Friday, April 5, 2024 - link

There were people saying this about ISA when the 32-bit PCI bus was introduced. People said it about 32-bit PCI when AGP slots became a thing. And not so shockingly, people said that about a previous PCIe generation each time a new standard was introduced.I'm not sure even a computing minimalist like me typing this on a Pentium n3700-powered laptop would be okay trying to push I/O at ISA speeds today so I would suggest caution in arguing a 7.0 spec won't become useful over its lifespan - assuming trace routing and signaling aren't overly problematic. If that is a problem, then it may just push computing technologies to exist on smaller and more highly integrated PCBs that use fewer lanes and solder down more previously slot-based components which is good in some ways, but it might endanger DIY hobbyists even moreso than has been the case of the last few years. Interestingly, building a desktop PC is almost boiling down to installing a CPU, memory, storage, and a graphics card into fairly idiot-proof shaped expansion slots anyhow and then fist pumping the air to feel like a technological champion so further integration isn't going to do too much harm. Those sorts of people will just fist pump plugging in their wireless keyboard dongle and an HDMI cable instead. Reply

DanNeely - Saturday, April 6, 2024 - link

The flip side is that PCIe 4 and 5 resulted in much more expensive mobos than PCIe3 and prior allowed. Another up-ratchet in costs could result in a significant delay or worse before they become offered on consumer systems as manufacturers try to figure out how to make hardware that can support them at non-datacenter price points. ReplyMagnus101 - Saturday, April 13, 2024 - link

There is a difference though. Many of your first examples were actual differences in different types of busses with enourmous uplifts at a time when there was an actual bottleneck in bandwidth.The last couple of updates in the PCIe standard have shown very little benefit.

Heck even the mighty 4090 will only loose 2% when using PCIe 3.0 instead of PCIe 5.0.

That is two generations apart with no perceivable difference for the historically most extreme consumer GPU(pricewise).

There is a manyfold generational disparity going on. Maybe in 3-4 generations of GPU:s from now we will reach saturationi for something like the current topend bus PCie 5.0. Reply

meacupla - Friday, April 5, 2024 - link

I disagree, but only because GPUs are too heavy. They need the length to keep them from snapping the connector even more than they currently do. ReplyDanNeely - Saturday, April 6, 2024 - link

There's no requirement that the electrical and physical connectors be the same size. We've already seen this with some lower end GPUs that are x16 physical but only x8 or x4 electrically. They take the bigger connector size for both mechanical mounting strength and to access the 75W slot power level only available for an x16 size card; but run fewer lanes to save cost on the PCB and GPU chips. Reply